Cortex-M7 MPU and default regions

Hi!

I would like to use the MPU on a STM32H743. As I saw in the app notes, the MPU has some default regions, that are active if the MPU is actually turned off.

For example, see page 5:

https://www.st.com/content/ccc/resource/technical/document/application_note/group0/08/dd/25/9c/4d/83/43/12/DM00272913/files/DM00272913.pdf/jcr:content/translations/en.DM00272913.pdf

If I use FreeRTOS MPU port, do I need to re-create these default settings using explicit MPU regions?

Or will this set of defaults always be “in the background”?

best regards

Thomas

Cortex-M7 MPU and default regions

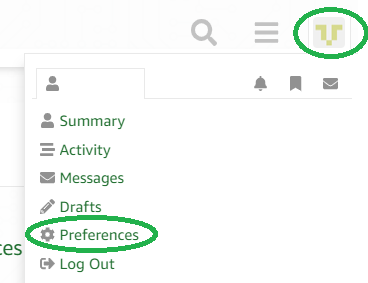

I don’t know about any chip specifics, but FreeRTOS always sets up the MPU in the same way, as described in the attached.

Cortex-M7 MPU and default regions

It’s not really chip specific..

The default addres map of the STM32H7 is defined in the ARMv7M Architecture Reference Manual:

https://static.docs.arm.com/ddi0403/eb/DDI0403EBarmv7m_arm.pdf

Chapter B3.1, page 648.

If I’m reading the document correctly, the default map is only active when the MPU is off.

So if I enable the MPU, I suspect I have to explicitly program the RAM cache regions, device memory attributes, etc. ?

The MPU document you have linked above seems to set only the read/write attributes, but not the cache bits (of course it’s written for a Cortex-M3, so that’s ok).

So what about Cortex-M7 chips with more complex MPUs?

Cortex-M7 MPU and default regions

I’m not sure if this addresses / answers your concern/question, but I believe that:

- When the MPU is enabled, if MPU_CTRL[PRIVDEFENA] is set to 1, any access to an address that is not in a defined MPU region acts as though it is going through the default map.

- When the MPU is enabled and MPU_CTRL[PRIVDEFENA] is set to 0, any access to an address that is not in a defined MPU region results in a fault (processor exception)

- If the MPU is not enabled, of course the default map is what’s used.

Cortex-M7 MPU and default regions

Thank you!

That was the missing piece I was looking for!